仿真 DDR3 IP Core 时的填坑方法汇总

很多朋友看了SDRAM第一季和第二季之后,希望能再来个SDRAM第三季讲一讲DDR3。

而DDR3的工作原理与SDRAM的工作原理基本一致,都有初始化和刷新的操作,在FPGA使用DDR3一般也都是调用其内部的 DDR3 IP Core。如果要录制一套DDR3的视频教程,其实说白了也就是带着一起看看 DDR3 IP Core 的 User Guide。

SDRAM第一季和第二季带着一起看手册,应该还是讲的比较详细了,有了之前的基础,DDR3 的 User Guide 相信也不难看懂。基于这些原因,便没有录制DDR3 的视频教程。

虽然 DDR3 IP Core 的 User Guide 讲得也还算详细,但可能想真正去掌握DDR3 IP Core 的用法,还需要自己去多仿真看看结果。

下面以 Xilinx spartan 6 系列的 DDR3 IP Core 仿真为例,结合咱们暑期线下FPGA培训班学员遇到的问题,给大家汇总下仿真 DDR3 IP Core 时的填坑方法。之后有时间再说说 7 系列的 DDR3 和 Altera 的 DDR3 。

一、学会使用官方的example_design

生成 DDR3 IP Core之后,在DDR3 IP 的生成目录,会有3个文件夹:docs、example_design、user_design。

在刚开始学 DDR3 IP Core 怎么使用的时候,可以直接用example_design里的文件,当然它里边也提供了仿真用的 testbench 文件。绝对可以说是一条龙服务。

咱们先把example_design的文件加进来仿真看下。

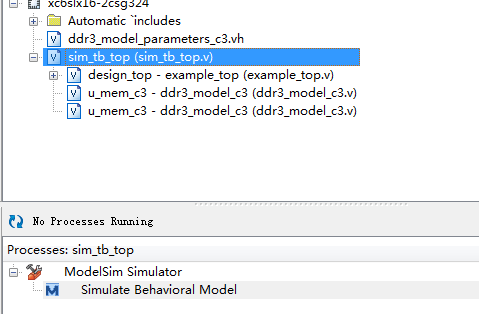

加入到 ISE 之后,模块间的层次结构大致就是这样子的了。

接下来双击 下边的仿真按钮就可以调用Modelsim进行仿真了。

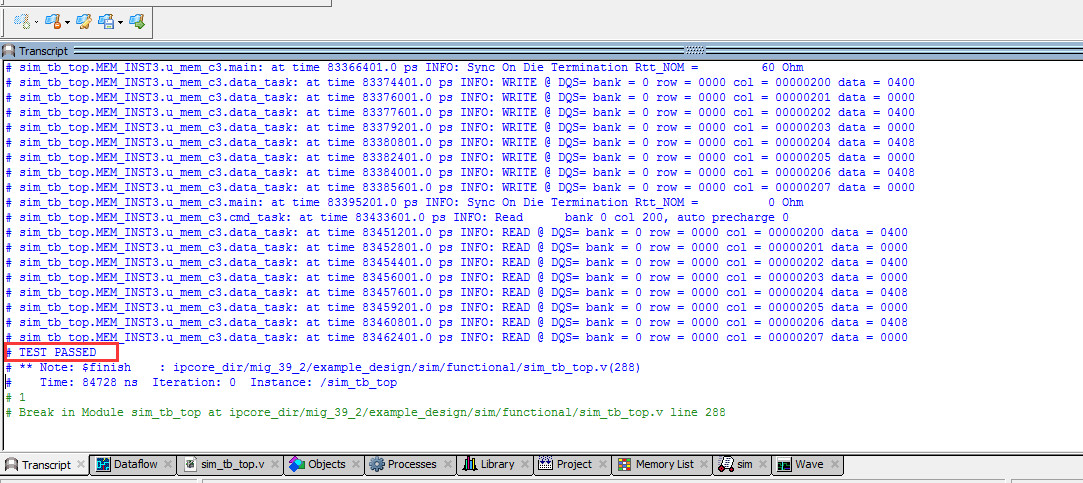

运行一段时间后,会看到 “TEST PASSED” 测试通过的信息。

如果不太清楚怎么使用DDR3 IP Core的朋友,完全可以先参看example_design来进行学习,有不清楚的结合文档,文档不明白的,再结合代码。这样学起来效率才高。

二、自己搭建 DDR3 IP Core 仿真平台

刚才咱们只是使用example_design 工程进行仿真,可能之后咱们想自己来搭建DDR3 的仿真平台,那应该怎么来做呢?

可以参考example_design 的 testbench 文件。

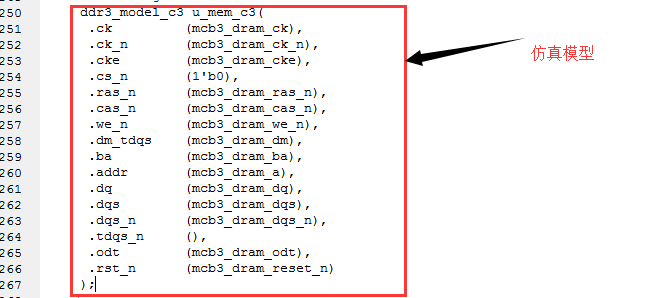

在example_design中,也带有ddr3 的仿真模型文件。关于怎么来连接DDR3 IP 与DDR3 相关的端口,完全可以参考example_design 的仿真文件。

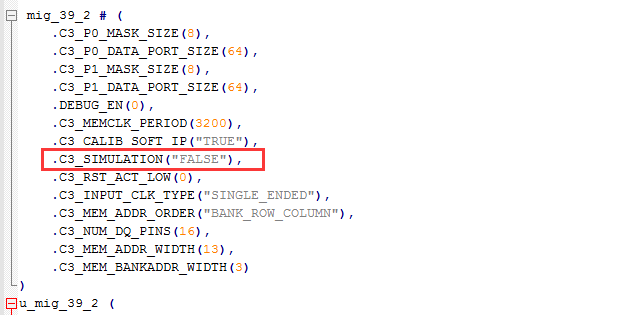

当然如果是自己搭建DDR3 IP Core的仿真平台,在例化IP Core的时候,可以把simulation的参数改为TRUE。

三、DDR3 IP Core的参考时钟

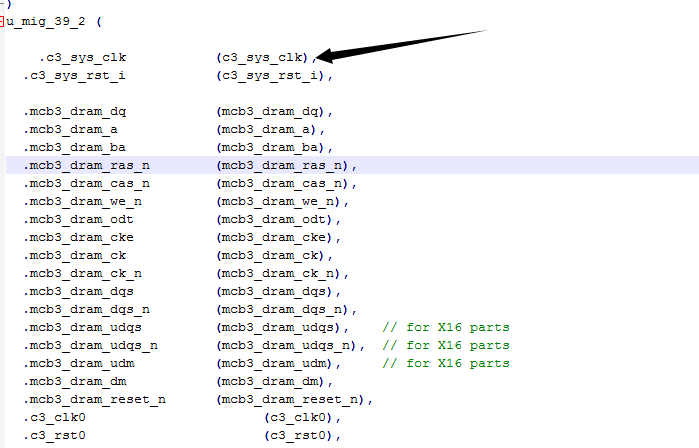

DDR3 IP Core需要由一个参考时钟,也就是图中的c3_sys_clk这个端口,这个端口需要由外部时钟提供,如果是用PLL给它提供是会报错的。

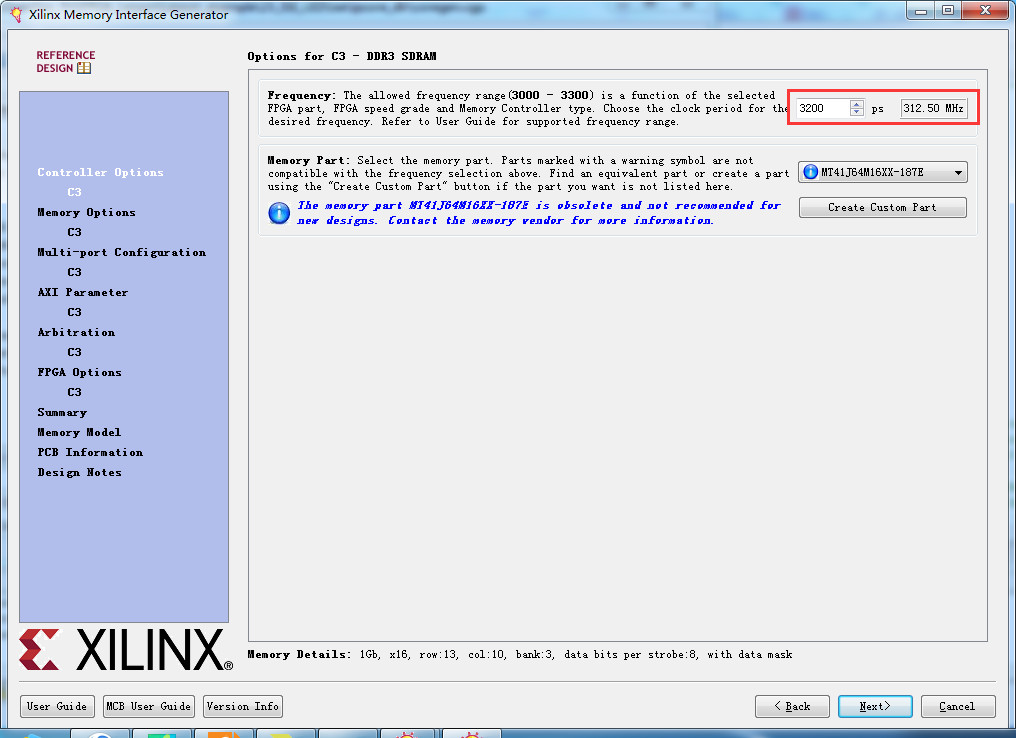

另外关于这个时钟的频率多高,对于Spartan 6,这个端口的参考时钟频率与DDR3 的工作时钟频率一致。而DDR3的工作时钟频率就是你在IP Core中设置的时钟频率。

在 IP Core中设置的是3200ps,也就是312.5MHz 。这个时钟频率,一方面是指DDR3芯片工作的时钟频率为312.5MHz,另一方面也是指它的c3_sys_clk默认的时钟频率也是312.5MHz。

如果是这样的话,DDR3芯片如果需要工作时钟频率为400MHz,那是不是也就意味着外部需要有一个400MHz的时钟呢?

假设你现在的板子,外部时钟只有一个50MHz的晶振,那怎么办呢?那是不是你的DDR3就只能工作在50MHz了呢?肯定是有方法解决的。

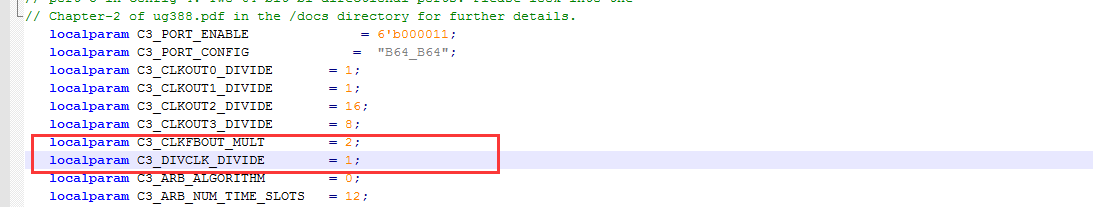

我们可以通过更改IP Core内部的PLL倍频与分频系数比。

也就是 C3_CLKFBOUT_MULT 和 C3_DIVCLK_DIVIDE 这两个系数。这两个系数默认为 2 和 1。

之前输入的参考时钟频率是312.5MHz,现在是换成输入50MHz的,它们俩之间相差12.5倍,可以把C3_CLKFBOUT_MULT 改为 25 , C3_DIVCLK_DIVIDE 改为 2。

先暂时通过这篇文章把 spartan 6 系列的DDR3 仿真问题汇总一下,后续有时间再介绍 Xilinx 7 系列的 DDR3 和 Altera 的 DDR3仿真问题。

Kevin

2019年10月15日 下午10:18

这个需要具体看你是把哪些信号 有 SET UP DEBUG. 但提示The debug hub core was not detected这个问题,应该不是你的 SET UP DEBUG导致的,是由于时钟没有跑起来,你可以看看DDR3 IP 的参考时钟是否稳定, 另外DDR3 IP 的复位是否正常释放,可以先看看这个,有问题可以加我私人微信:opensoc888