SOC从此开始,初探ZYNQ的DMA传输

很久都没有写文章了,一直想写一篇关于SOC的文章,始终没有想好到底该写什么。

如果说写个串口显示的 “Hello World!”,那就太简单了!

正好最近在弄ZYNQ的SOC图像处理,用到了DMA传输,便决定来写第一篇关于SOC的文章,用第一篇文章来简单的介绍一下DMA传输。

当然,这里还是解释一下什么是DMA,全称Direct Memory Access,直接内存存取。它是一种几乎不需要CPU干预的一种内存访问方式,当然这里的内存指的是DDR3。

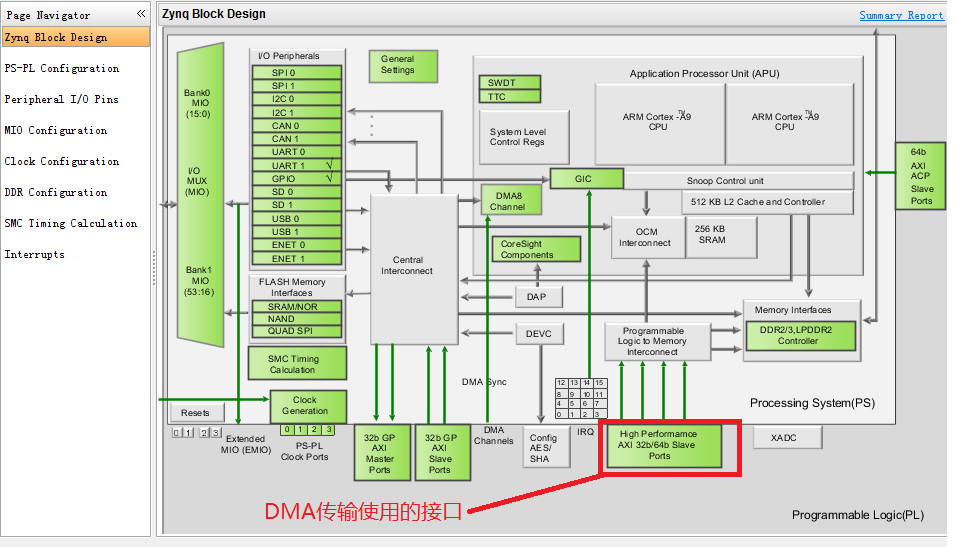

ZYNQ的PL和PS进行DMA传输时,使用到的是High Performance AXI4 32bit/64bit Slave Ports。

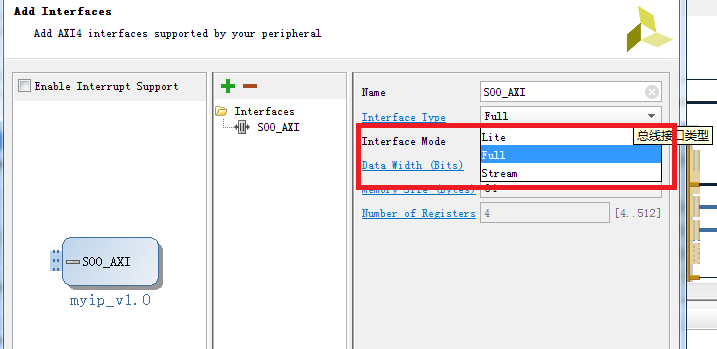

在进行DMA传输时,使用到的是AXI4协议。当然AXI4协议也有很多种,在我们使用Vivado创建自定义IP的时候就可以看到接口类型有:Lite、Full、Strem这三种。

在进行DMA传输时,使用的是Full这个接口类型。该接口支持突发方式的读写模式。

Lite类型,是不支持突发模式的,一般应用场景在于PS对某些寄存器的配置,传输少量的数据信息。

Stream类型,也是一种大数据量的传输接口,但是它没有相关的读写地址接口,是一种数据流模式的传输方式。在Xilinx的很多IP Core中,都有这个接口的身影。

好了,废话不多说了。我们来看一下演示的这个例子。

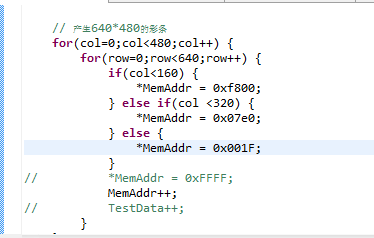

首先,我们在PS端向DDR3中写入了640*480个16bit的数据,来模拟一幅图像的数据量。

当然,这里产生的数据,大家应该可以看出,模拟的图像,是3个彩条。

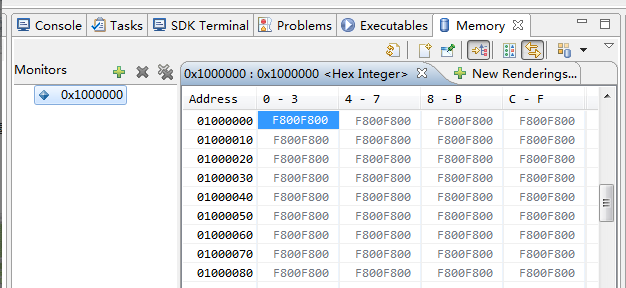

运行之后,也可以查看到DDR3中已经写入了我们想要的数据。

在DMA读模块工作之后,可以看到显示上也显示了彩条。

是的,效果实现了,那DMA传输它到底是怎么工作的呢?

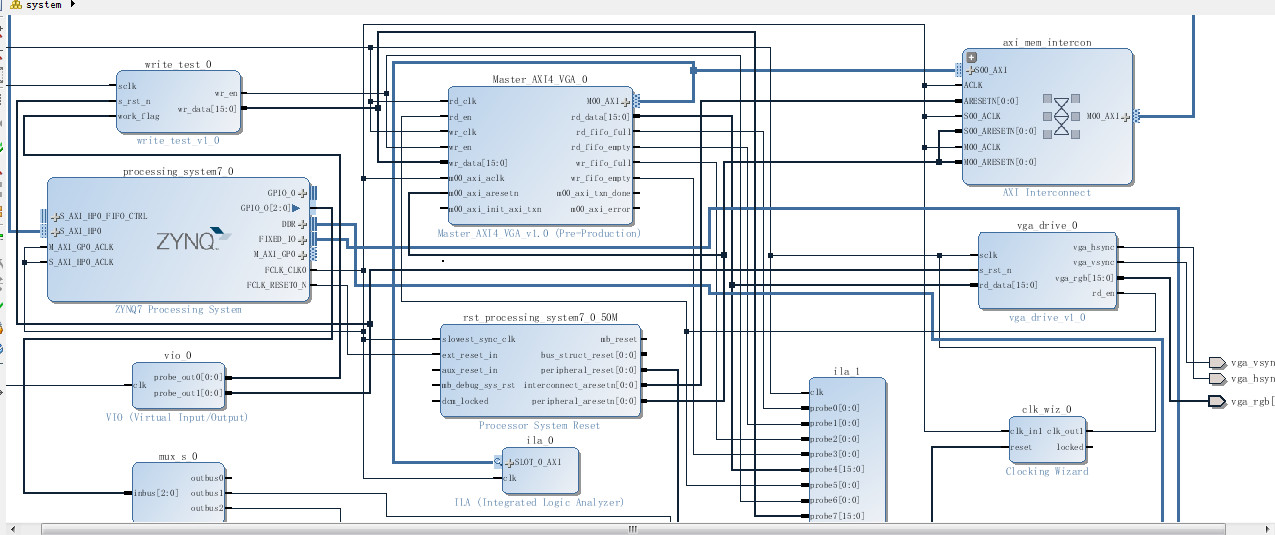

先来看一下SOC的硬件框架,也就是Block Design的框架。

Master_AXI4_VGA_0这个模块,集成了DMA读和写的功能,VGA显示的画面,就是该模块通过DMA读操作,读取到了DDR3中的数据。

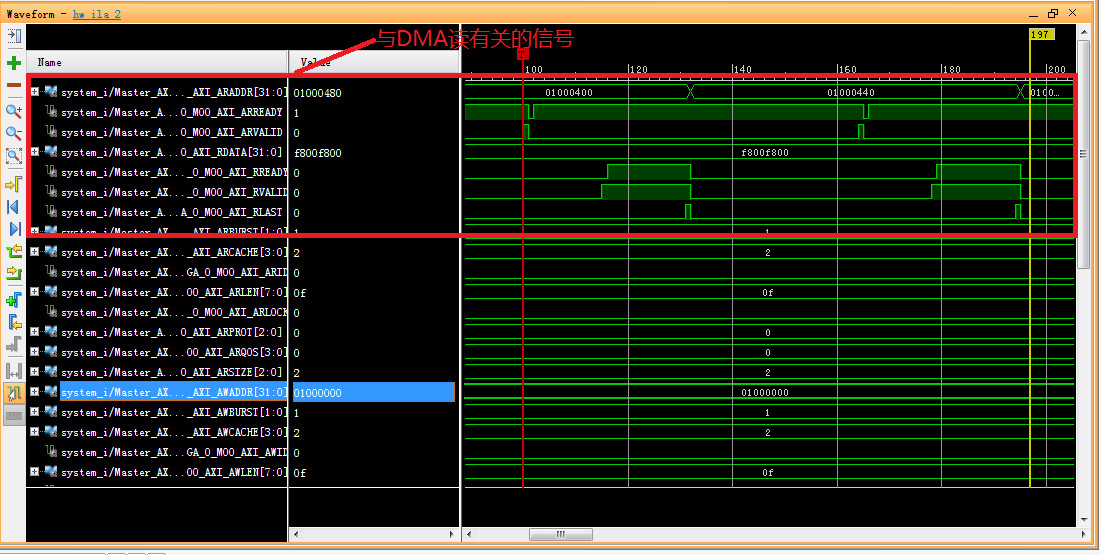

这是通过ILA抓取到的DMA读操作波形图,图中可以看到读出的数据为32’hF800F800,这是因为HP AIX4接口使用的是32bit,而且设置的突发长度为16。

当然这个只是DMA的读操作,下边来说一下DMA的写操作。

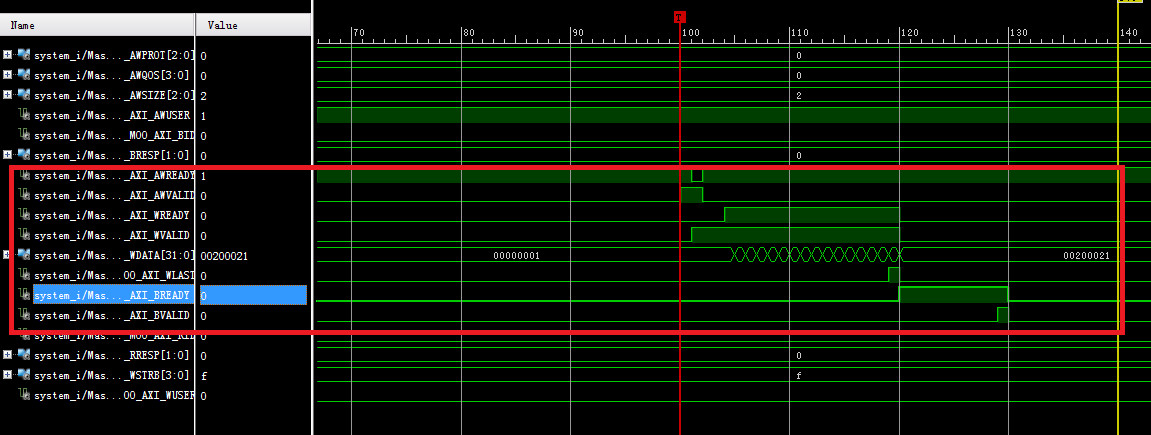

DMA写操作,在外部有一个写数据的测试模块write_test_0,该模块产生递增的写数据。

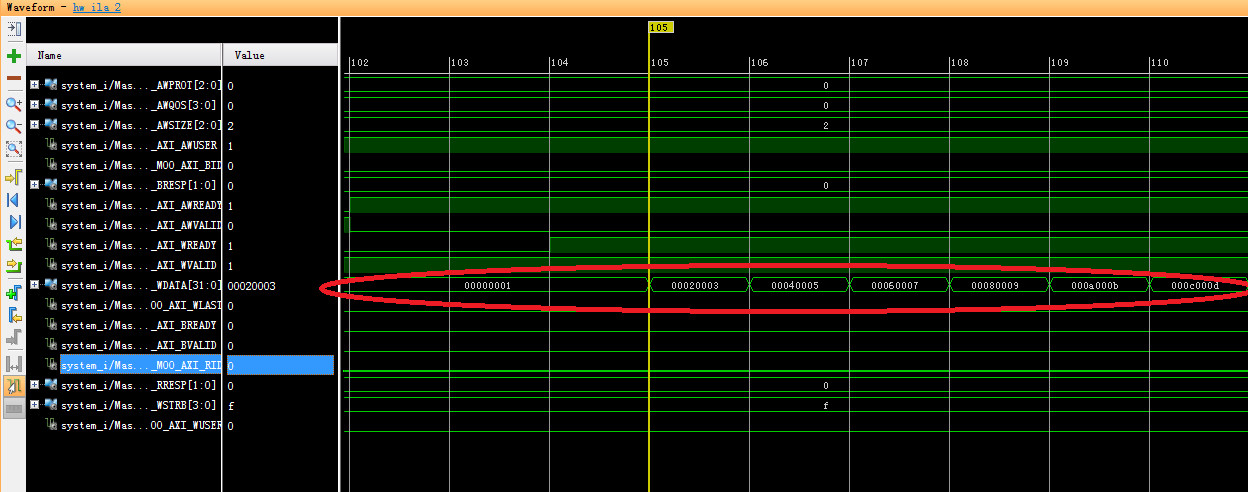

这是通过ILA抓到的与DMA写操作相关的信号,将写入的数据放大一点来看,是按照32‘h00000001,32’h00020003这样的数据拼起来的。

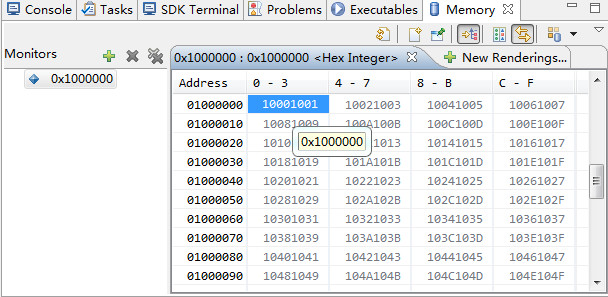

那我们再在SDK中看一下DDR3中的数据是怎么样的呢?

数据也是按照这种格式排列的,当然这里看到的数据与ILA中抓到的数据不一样,是因为咱们不是在同一时刻抓取的。

最后再来看一下VGA显示上显示的效果。

当然,通过VGA的效果,我也不知道这个效果是不是递增数展现的一个效果,但可以说明,DMA读和写的功能是已经实现了的。

总结一下,这篇文章只是简单的给大家介绍了DMA的工作过程,至于AXI4的时序关系,因为网上已经有太多的资料了,故没有作太多的介绍。

DMA的读和写功能已经实现了,然后再在目前的这个硬件平台上挂上一个摄像头,实现SOC的摄像头显示系统也不是难事了。

基于SOC的摄像头显示系统完成了,摄像头的数据能正确的写入到DDR3中,之后便可以在PS端做其他的图像处理算法,做基于深度学习的人脸检测等其他高深的应用。

在Kevin的下一篇文章中,将会介绍,如何在ZYNQ中将摄像头的数据写入到SD卡中,也就是实现一个类似于拍照的功能。

相关阅读:

Xilinx reVISION堆栈下开发体验(一)【资料篇】