【开源骚客】《轻松设计SDRAM控制器》第八讲—命令解析模块讲解

到第七讲,我们就已经把SDRAM控制器的部分全部都完成了。

虽然SDRAM控制器的部分完成好了,但是咱们的项目还没完,我们还需要将串口部分和控制器部分联合起来,形成一个可以通过串口发送命令控制SDRAM读写的完整项目。

在第三讲中,我们已经完成了串口的收发功能。在本讲中,我们先来对串口发送过来的命令和数据进行解析和分离。

在搞定读模块之后,就相当于SDRAM控制器部分已经搭建好了,想一想还是很期待的哦,哈哈,大家先别急。在这一讲中,我们就来完成读模块,然后对这个SDRAM控制器稍加完善就可以应用到项目中了。

本讲主要内容如下:

- 命令解析模块的作用详细介绍;

- 命令解析模块时序设计;

- 命令解析模块代码编写及仿真验证。

一、命令解析模块的作用详细介绍

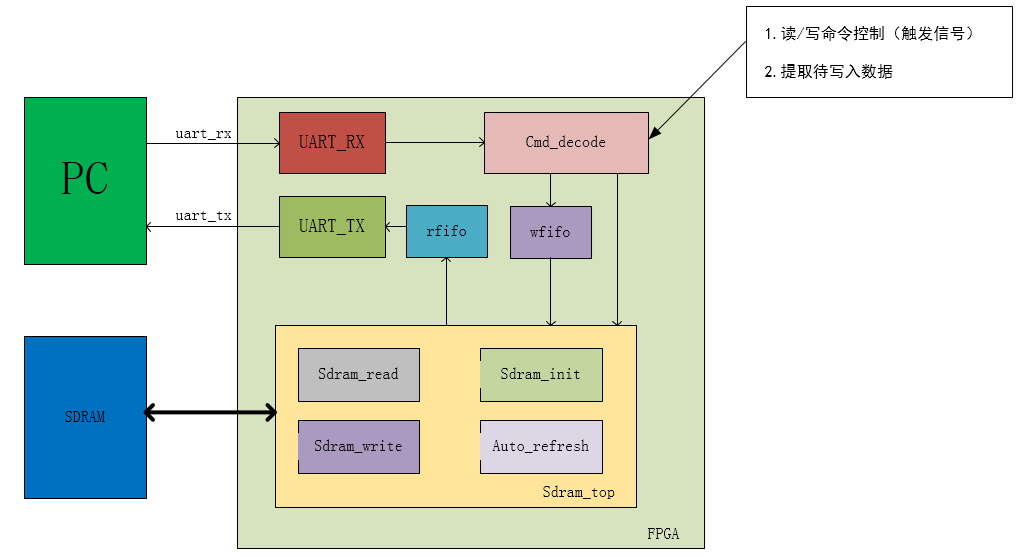

我们先回顾下在第一讲中所介绍到的项目整体框架图:

命令解析模块是将串口和SDRAM控制器联系在一起的一个桥梁,它会根据串口接收到的读/写命令产生相应的读/写命令控制(触发信号),并且也会从数据包中提取待写入到SDRAM中的数据。

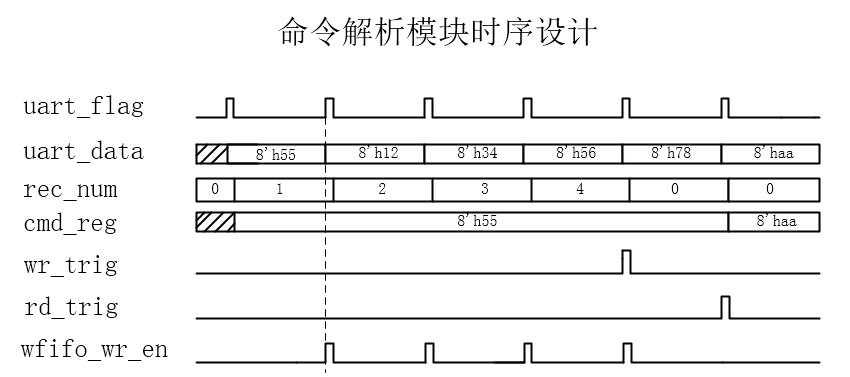

二、命令解析模块时序设计

对于这种时序图,相信大家跟着Kevin的视频早就掌握了看的方法,在此就不做介绍了,也给大家留下学习的空间。

三、命令解析模块代码编写及仿真验证

对于代码,Kevin还是一贯的作风,不会轻易贴出代码的,但是这个命令解析模块的功能还是相对比较简单的,为了让大家能把自己的代码和Kevin的代码进行对比,Kevin还是找了很多扯淡的理由(内心十分煎熬啊)去说服自己把代码贴出来。

module cmd_decode(

// system signals

input sclk ,

input s_rst_n ,

// From UART_RX module

input uart_flag ,

input [ 7:0] uart_data ,

// Others

output wire wr_trig ,

output wire rd_trig ,

output wire wfifo_wr_en ,

output wire [ 7:0] wfifo_data

);

//====================================================================\

// ********** Define Parameter and Internal Signals *************

//====================================================================/

localparam REC_NUM_END = 'd4 ;

reg [ 2:0] rec_num ;

reg [ 7:0] cmd_reg ;

//==========================================================================

// *************** Main Code ****************

//==========================================================================

always @(posedge sclk or negedge s_rst_n) begin

if(s_rst_n == 1'b0)

rec_num <= 'd0;

else if(uart_flag == 1'b1 && rec_num == 'd0 && uart_data == 8'haa)

rec_num <= 'd0;

else if(uart_flag == 1'b1 && rec_num == REC_NUM_END)

rec_num <= 'd0;

else if(uart_flag == 1'b1)

rec_num <= rec_num + 1'b1;

end

always @(posedge sclk or negedge s_rst_n) begin

if(s_rst_n == 1'b0)

cmd_reg <= 8'h00;

else if(rec_num == 'd0 && uart_flag == 1'b1)

cmd_reg <= uart_data;

end

assign wr_trig = (rec_num == REC_NUM_END && cmd_reg == 8'h55) ? uart_flag : 1'b0;

assign rd_trig = (rec_num == 'd0 && uart_data == 8'haa) ? uart_flag : 1'b0;

assign wfifo_wr_en = (rec_num >= 'd1) ? uart_flag : 1'b0;

assign wfifo_data = uart_data;

endmodule