【开源骚客】《轻松设计SDRAM控制器》第五讲—仲裁机制介绍及刷新模块讲解

对于很多刚接触SDRAM的朋友来说,还不能完整的设计出SDRAM控制器,很大一部分原因就是没了解到仲裁机制。

仲裁机制应该是说SDRAM控制器中最关键的部分,理解并掌握仲裁机制对于设计SDRAM控制器是至关重要的一点。

讲完第五讲之后,整个SDRAM控制器的各模块就可以说很清晰了。特别是掌握了仲裁机制后,对于SDRAM的刷新操作、写操作、读操作三个操作之间的控制也可以非常流畅的控制起来了。所以在第五讲中,我们会全面的给大家介绍仲裁机制,并且会把仲裁模块与刷新模块间的联系毫无保留的分享给大家(此处应有掌声啊!!!嘻嘻。。)。

本文主要内容如下:

- SDRAM刷新知识普及;

- SDRAM仲裁机制介绍;

- SDRAM刷新模块讲解;

- 仲裁模块与刷新模块编写。

一、SDRAM刷新知识普及

在第四讲中,我们已经介绍到了,SDRAM需要不断的刷新来给SDRAM中存储数据的电容充电来达到数据不丢失的目的。

那问题来了,SDRAM每两次刷新的间隔是多长时间呢,SDRAM中的所有存储单元是同时刷新的吗?这些我们都不知道,所以就需要看官方的手册了。

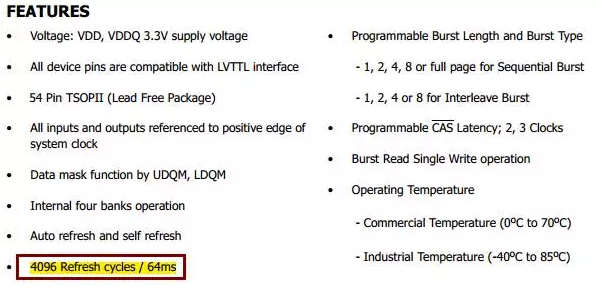

在手册上,有4096 Refresh cycles / 64ms。

我们先解释下他的意思,64ms是电容在未充电的状态下能保持电量的最长时间,也就是SDRAM在未刷新的状态下能保存数据的最长时间是64ms。

4096,指的是在64ms的时间里边需要刷新4096次。为什么是4096次呢?因为SDRAM刷新是一行一行进行的,而控制行地址的总线有12bit,也就是一个Bank有4096行咯。第一刷新第0行和第二刷新第0行的时间不能超过64ms,但是需要在这个时间中刷新4096行,所以就需要刷新4096次了哦。。

所以,每两次刷新的时间间隔大约是64ms / 4096 = 15.625us。在本项目中,我们设置刷新间隔为15us。

二、SDRAM仲裁机制介绍

在前边我们已经了解到,SDRAM有三种必需的操作:刷新操作、读操作和写操作。

这三种操作之间的协调及相互转换怎么来处理呢?所以就引入了“仲裁机制”。

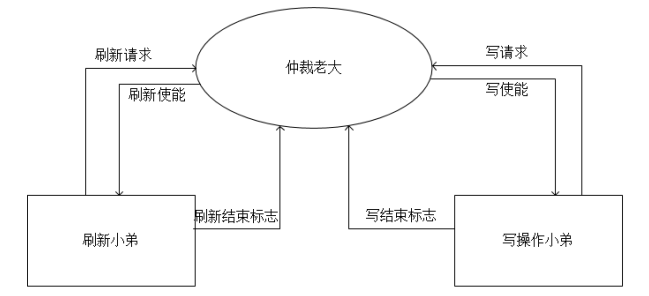

以刷新操作为例:当刷新的时间到了之后,刷新模块向仲裁发起刷新请求,然后仲裁老大根据SDRAM当前所处的一个状态来判断是否可以允许SDRAM进行刷新,当仲裁老大认为SDRAM可以刷新了之后,向刷新模块给出刷新使能信号;当刷新模块对SDRAM进行刷新完毕后,再向仲裁老大给出刷新结束标志。

其实这个图也可以是SDRAM控制器各个模块的划分与连线图了。

写操作和读操作与仲裁之间的联系,和刷新操作与仲裁之间的联系完全相同。

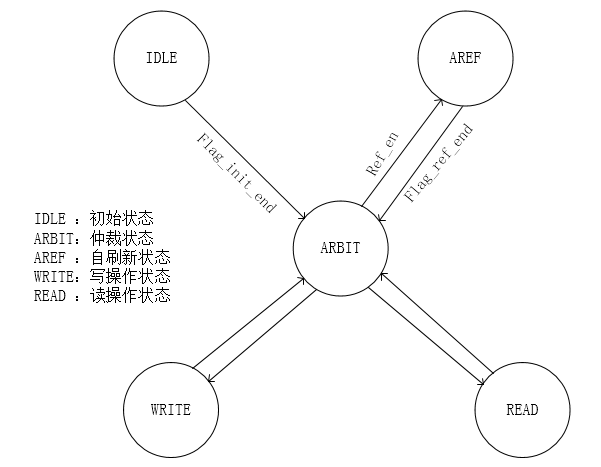

对于模块内的状态机设计如下图:

大家刚接触这种状态图可能还不太理解,不过没关系,在咱们的视频教程中有详细的解释。而且设计的状态机也是按照这个状态图来的。

(视频观看地址:http://t.elecfans.com/1418.html,当然也可以访问开源骚客的官网http://www.opensoc.cn或Kevin的个人博客http://dengkanwen.com获取更多的学习干货)

三、SDRAM刷新模块讲解

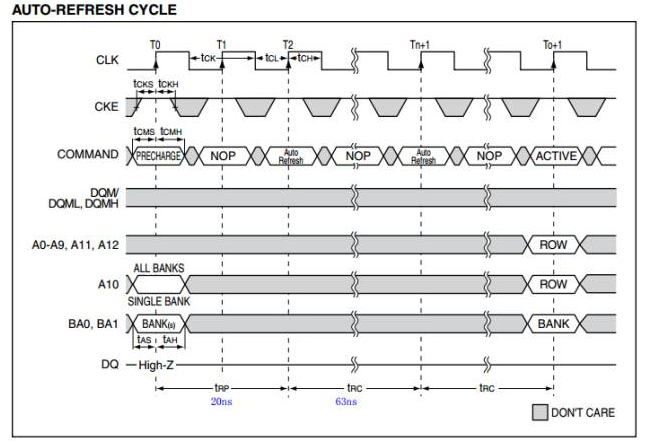

这就是刷新操作的时序图了,关于图中的参数,大家都可以在手册中找到,在此就不做介绍了。

四、仲裁模块与刷新模块编写

对于仲裁模块与刷新模块的编写,Kevin一般都不太习惯直接给出代码,否则就会把正在学习SDRAM的你们引入到我自己的思路。所以Kevin在此不贴出代码,而且Kevin也相信,有我们前面对理论知识的介绍,认真学习的你们肯定是可以跟上我们教程的节奏,

Good Luck!!!!!!!!!!!